计算机组成原理笔记(二)

第四章 指令系统

指令周期

指令周期是指取出一条指令并执行这条指令的时间。一般由若干个机器周期组成,是从取指令、分析指令到执行完所需的全部时间。

指令字的地址格式(掌握指令、指令字概念、格式)

指令(机器指令):控制计算机执行某种操作的命令。

一条指令中通常包含以下信息:

- 操作码:用来指明该指令要完成的操作

- 操作数:用来指明操作数的地址

- 操作结果的存储地址

- 下一条指令的地址

从上述信息可知,指令字是用来描述一条指令的机器语言代码。指令字由操作码和地址码组成。

寻址方式

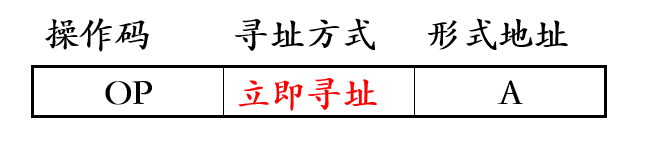

1.立即寻址

指令字中的地址码部分直接给出操作数,而不是操作数的地址。取出指令的同时也取出了操作数,无需访问主存

例如:#1000H

2.直接寻址

地址码部分直接给出操作数在内存中的有效地址EA。执行指令时,需访问一次主存存取操作数

例如:1000H

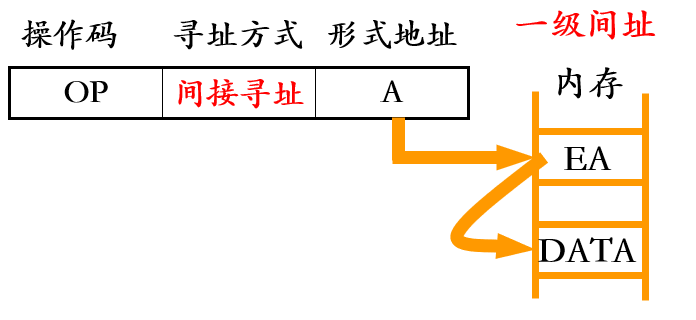

3.间接寻址

指令字中的地址码部分给出的是操作数地址的地址(形式地址,不是操作数的真正地址)或是指示操作数地址的地址指示字。需访问主存两次

例如:(1000H)

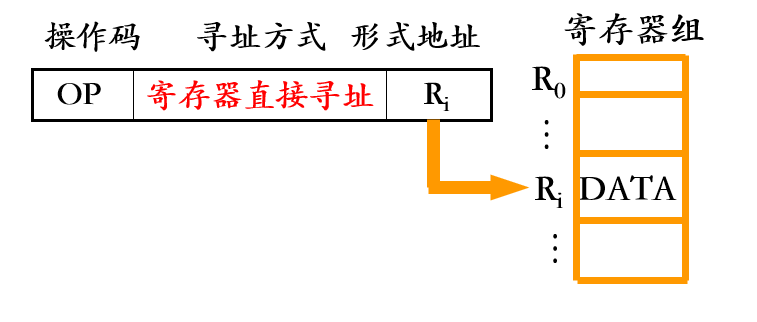

4.寄存器直接寻址(寄存器寻址)

指令字中的地址码部分给出某一通用寄存器号,该寄存器的内容即为指令所需的操作数。操作数在寄存器中,无需访问主存,速度快

例如:R1

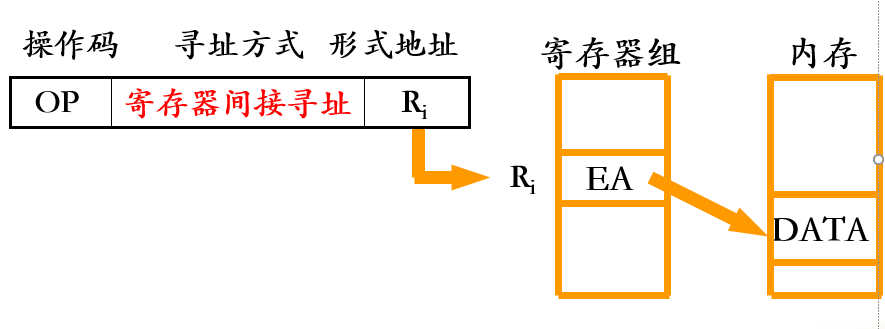

5.寄存器间接寻址

指令字中的地址码部分所指定的寄存器中内容是操作数在内存中的有效地址。先访问寄存器取得操作数在内存的有效地址,再访问主存,取得操作数。需访问主存1次

例如:(R1)

6.相对寻址

有效地址EA=(PC)+A

程序寄存器PC

7.变址寻址

有效地址EA=(Ri)+A

变址寄存器Ri

8.基址寻址

有效地址EA=(Rb)+A

机制寄存器Rb

第五章 控制器和CPU

控制器主要功能与基本组成

主要功能就是根据事先编好并存放在存储器中的解题程序,按所执行指令的具体要求,适时地产生并发出各种控制命令,控制计算机各部件自动、连续、协调地进行工作,直到完成程序的全部功能为止。所以控制器的基本功能就是运行程序。

主要组成:

1.指令寄存器IR:存放当前正在执行的指令

2.程序计数器PC:存放即将执行的指令的地址

3.时序部件

4.控制信号发生器

控制器实现的两种方式

1.组合逻辑型(硬联逻辑、硬布线逻辑)

2.存储逻辑型——微程序控制器

CPU中各个主要寄存器及其功能(每个寄存器表示什么)

AR: 地址寄存器 DR: 数据寄存器 RX: 暂存目的操作数 RY: 暂存源操作数微指令操作控制字段的编码方式

- 直接控制法(不译法)

- 最短编码法

- 字段直接编码法

- 字段间接编码方式

流水线的分类

- 按处理级别分类

- 操作部件级流水线

- 指令级流水线

- 处理机级流水线

- 按功能分类

- 单功能流水线:只完成一种功能

- 多功能流水线:可完成两种以上功能

- 按工作方式分类

- 静态流水线

- 动态流水线

- 按流水线结构分类

- 线性流水线

- 非线性流水线

流水线的性能指标

主要指标有3个:吞吐率、效率和加速比 。

流水总时间公式

n为指令数

第六章

外设的两种编址方式

1.统一编址

2.独立编址

磁盘的记录面、磁道、柱面、扇区、扇段等概念

- 记录面(盘面):磁盘片表面称为记录面。盘片的上下两面都能记录信息。

- 磁道(柱面):记录面上一系列同心圆。每个盘片表面通常有几十到几百个磁道。

- 磁道的编址:从外向内依次编号,最外一个同心圆叫0磁道,最里面的一个同心圆叫n磁道,n磁道里面的圆面积不用来记录信息。

- 扇区:将盘面沿垂直于磁道的方向划分成若干个扇区。

- 扇段:每条磁道在扇区内的部分称为扇段,每个扇段存储等量的信息。扇段是磁盘信息的基本单位。由于各条磁道的半径不同,各条磁道的存储密度不同。外圈存储密度低,内圈存储密度高。

磁盘的主要性能指标

①存储容量C

存储容量指磁盘组所有盘片能记录的二进制信息的最大数量,一般以字节为单位。

②平均寻址时间

平均寻址时间=平均磁道定位时间+平均旋转等待时间

③平均存取时间TA

④存储密度

⑤数据传输率Dr

⑥误码率

⑦价格

中断的概念(中断的五个步骤)

概念:处理机中止现行程序的执行,而转去执行处理更为紧迫事件的服务程序,待处理完毕后再自动返回执行原来的程序,这一过程称为中断。

五个步骤:

中断请求的条件、优先级

- 准备就绪

- 设备未被屏蔽

若新的中断的优先级高于原中断的优先级,CPU响应新的中断;否则,CPU不予响应,必须待原中断处理完毕且返回主程序后,再响应新的中断。

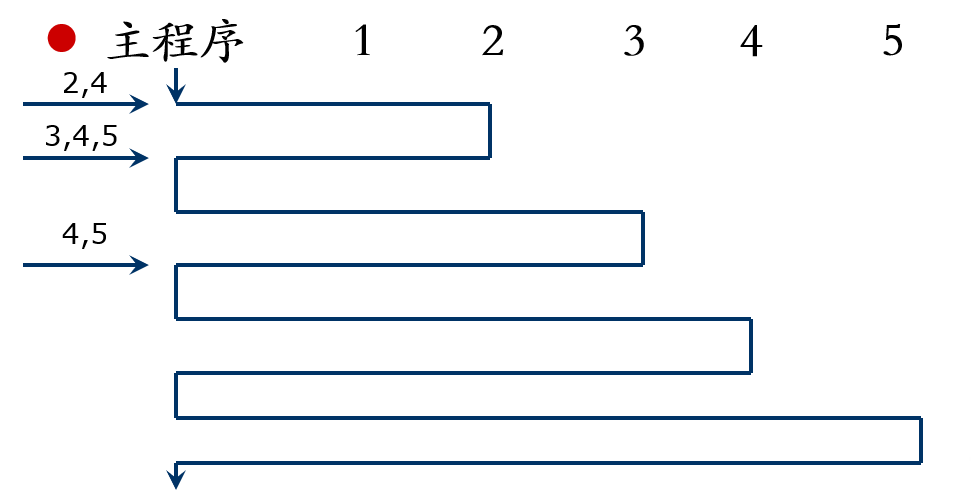

例1.某计算机的中断系统有五级中断,优先次序为1->2->3->4->5 若CPU在执行正常程序时,有下列事件发生:

(1) 中断2,4 提出请求;

(2) 在处理中断2过程中,又有中断3 ,5提出请求;

请画出CPU对所有事件的处理过程图及其屏蔽字。

DMA基本概念及传送过程(重点掌握周期挪用方式,CPU暂停方式)

DMA方式的实质是以主存为中心,采用硬件手段在主存与I/O设备之间建立直接的数据传送通路,由DMA控制器(DMAC)取得总线控制权,控制主存与I/O设备之间的数据传送,在传送过程中不需要CPU的干预。

DMA传送方式

1、CPU暂停方式

当DMA设备需要与主存交换信息时,由DMAC向CPU发总线请求,CPU响应请求后,暂停工作并让出总线的控制权。DMAC取得总线控制权,控制设备与主存之间的信息传送,直到一批数据全部传送完毕,再将总线使用权交还给CPU。

2、周期挪用方式(周期窃取方式)

外设每准备好一次数据传送,由DMAC向CPU发出总线请求,CPU响应后让出一个或几个主存周期,DMA控制器取得总线控制权,控制设备与主存之间的一次数据传送。

程序中断与DMA的比较

1、程序中断是以CPU为中心,采用软硬件结合的技术手段,控制设备与主机之间的数据传送。

DMA方式是以主存为中心,采用硬件手段,控制设备与主存间直接进行数据传送。

2.程序中断需要进行程序切换,所以需要保存与恢复现场。DMA方式由DMA控制器直接控制数据传送。在数据传送期间,不需要CPU干预,所以不需保存与恢复现场。

3、程序中断适合于慢速外设;DMA适合于快速外设。

4、程序中断必须在一条指令执行结束后才能响应。DMA在一个主存周期结束后即可响应。

5、程序中断可实现多种处理功能;DMA仅用于主存与设备之间的数据传送。

第七章 总线

总线概念及性质

概念:一组可为多个功能部件共享的公共信息传送线路。

总线上信息传输的特点:某一时刻只允许一个部件向总线发送信息,而多个部件可同时从总线商接收信息。

总线的分类(按传输信息)

地址总线;数据总线;控制总线

总线的连接方式(各种方式下总线结构的特点)

(1) 单总线结构

(2) 双总线结构

① 面向主存的双总线结构

② 以CPU为中心的双总线结构

(3) 三总线结构

(4) 通道

总线仲裁的方法(掌握集中式仲裁的三种方式及特点)

- 集中式仲裁

1.链式查询:敏感性低

2.计数器定时查询:敏感性较高,可以改变优先级

3.独立请求方式:敏感性高 - 分布式仲裁